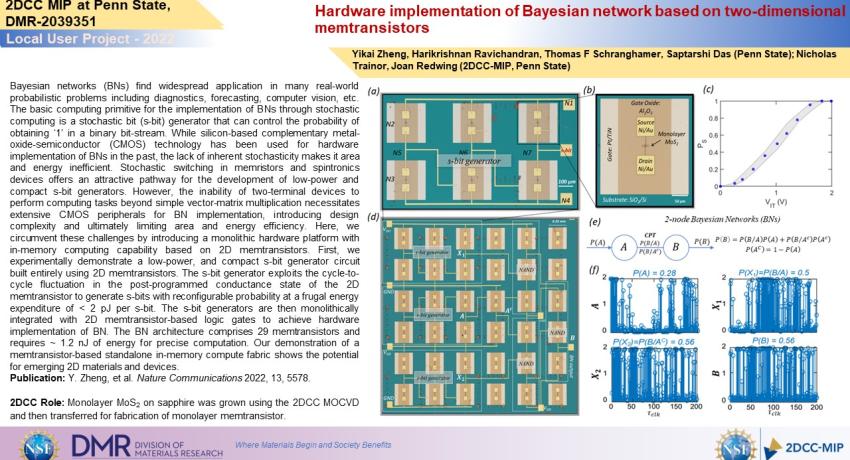

Bayesian networks (BNs) find widespread application in many real-world probabilistic problems including diagnostics, forecasting, computer vision, etc. The basic computing primitive for the implementation of BNs through stochastic computing is a stochastic bit (s-bit) generator that can control the probability of obtaining ‘1’ in a binary bit-stream. While silicon-based complementary metal-oxide-semiconductor (CMOS) technology has been used for hardware implementation of BNs in the past, the lack of inherent stochasticity makes it area and energy inefficient. Stochastic switching in memristors and spintronics devices offers an attractive pathway for the development of low-power and compact s-bit generators. However, the inability of two-terminal devices to perform computing tasks beyond simple vector-matrix multiplication necessitates extensive CMOS peripherals for BN implementation, introducing design complexity and ultimately limiting area and energy efficiency. Here, we circumvent these challenges by introducing a monolithic hardware platform with in-memory computing capability based on 2D memtransistors. First, we experimentally demonstrate a low-power, and compact s-bit generator circuit built entirely using 2D memtransistors. The s-bit generator exploits the cycle-to-cycle fluctuation in the post-programmed conductance state of the 2D memtransistor to generate s-bits with reconfigurable probability at a frugal energy expenditure of < 2 pJ per s-bit. The s-bit generators are then monolithically integrated with 2D memtransistor-based logic gates to achieve hardware implementation of BN. The BN architecture comprises 29 memtransistors and requires ~ 1.2 nJ of energy for precise computation. Our demonstration of a memtransistor-based standalone in-memory compute fabric shows the potential for emerging 2D materials and devices.

Publication: Y. Zheng, et al. Nature Communications 2022, 13, 5578.

2DCC Role: Monolayer MoS2 on sapphire was grown using the 2DCC MOCVD and then transferred for fabrication of monolayer memtransistor.

What Has Been Achieved: In this study, we have fabricated a standalone in-memory stochastic computing architecture utilizing 29 MoS2 memtransistors for the hardware implementation of Bayesian networks.

Importance of the Achievement: Here we have experimentally demonstrated a low-power, and compact stochastic bit (s-bit) generator circuit built entirely using 2D memtransistors and monolithically integrated the s-bit generators with 2D memtransistor-based logic gates to achieve hardware implementation of BN at an energy expenditure of 1.2 nJ of energy for precise computation.

Unique Feature(s) of the MIP that Enabled this Achievement: 2DCC-MIP’s MOCVD growth of high-quality, wafer-scale MoS2 films. The growth of high-quality monolayer MoS2 films enabled us to fabricate medium-scale integrated circuits for hardware implementation of Bayesian networks.

Publication: Yikai Zheng, Harikrishnan Ravichandran, Thomas F Schranghamer, Nicholas Trainor, Joan Redwing, Saptarshi Das. Hardware implementation of Bayesian network based on two-dimensional memtransistors. Nature Communication 2022, 13 (1), 5578. DOI: 10.1038/s41467-022-33053-x.

Acknowledgements: The work was supported by Army Research Office (ARO) through Contract Number W911NF1920338 and National Science Foundation (NSF) through a CAREER Award under grant no. ECCS-2042154.. Authors also acknowledge the materials support from the National Science Foundation (NSF) through the Pennsylvania State University 2D Crystal Consortium–Materials Innovation Platform (2DCC-MIP) under NSF cooperative agreement DMR-2039351.